|                  | Bipolar IC |

|------------------|------------|

| Preliminary data |            |

| Туре     | Ordering code | Package |

|----------|---------------|---------|

| SDA 3002 | Q67000-A2267  | DIP 18  |

Combined with a VCO (tuner) and a fast divider (dividing ratio 1:64), the ASBC technology component forms a digitally programmable phase-locked loop for television sets with PLL frequency synthesis tuning. The PLL enables crystal-controlled setting of the tuner oscillator frequency for 125 kHz resolution in the TV band III/IV/V. A serial interface facilitates connection to a microprocessor. The microprocessor loads the divider and the band select outputs with the appropriate information. The PLL provides status information (locked/unlocked) at output LOCK.

#### **Features**

- No external integrator required

- Noise-immune message transmission

- Software-controlled integration time constant

- Microprocessor-compatible

| Maximum ratings Supply voltage range                                                                                                                                 | $V_{\mathrm{S}}$                                                                                                       | -0.3 to 7.5                                                                              | V                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|

| Inputs Q1, Q2, $I_{\mathrm{REF}}$ IFO, CPL PLE F, $\overline{\mathrm{F}}$                                                                                            | V <sub>i</sub><br>V <sub>i</sub><br>V <sub>i</sub>                                                                     |                                                                                          | V<br>V<br>V                 |

| Outputs PD V <sub>0</sub> BS, VHF, UHF, Bd I/III, standard LOCK Junction temperature Storage temperature range                                                       | $egin{array}{c} V_{ m q} & V_{ m q} & I_{ m q} \ V_{ m q} & I_{ m q} & I_{ m q} \ I_{ m f} & I_{ m stg} & \end{array}$ | -0.3 to V <sub>S</sub><br>-0.3 to 33<br>-7<br>-0.3 to 16<br>-1 to 5<br>140<br>-40 to 125 | V<br>WA<br>V mA<br>°C<br>°C |

| Thermal resistance (system-air)                                                                                                                                      | R <sub>th SA</sub>                                                                                                     | 80                                                                                       | K/W                         |

| Operating range Supply voltage Input frequency Divider factor Resistance for $I_{REF}$ $I_{REF} = (V_S - 0.8) R_i$ Tuning voltage open collector Ambient temperature | Vs<br>f <sub>F</sub> , f <sub>F</sub><br>N<br>R <sub>i</sub><br>V <sub>D</sub>                                         | 4.5 to 7.15<br>16<br>1024 to 16383<br>80<br>0.3 to 33                                    | V<br>MHz<br>kΩ<br>V<br>°C   |

| Characteristics $V_S = 5 \text{ V}; T_A = 25 ^{\circ}\text{C}$                                 |                                      |       |     |                     |          |

|------------------------------------------------------------------------------------------------|--------------------------------------|-------|-----|---------------------|----------|

| 15 0 1, 1, 20 0                                                                                |                                      | min   | typ | max                 |          |

| Supply current                                                                                 | $\overline{I_{S}}$                   | 15    | 22  | 35                  | mA       |

| Signal inputs F/F                                                                              |                                      |       |     |                     |          |

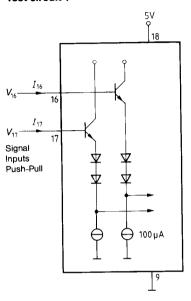

| Input voltage                                                                                  | V <sub>16H</sub><br>V <sub>16L</sub> | 3.8   |     | V <sub>S</sub> +0.2 | V        |

| Input current $V_{16} = 5 \text{ V}$                                                           | $I_{16}$                             |       |     | 50                  | μА       |

| Input sensitivity at sine push-pull; f = 16 MHz (peak-to-peak)                                 | V <sub>16pp</sub>                    | 120   |     | 1200                | mV       |

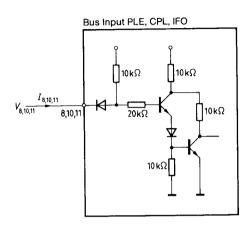

| Inputs (IFO, CPL, PLE) Input voltage                                                           | $V_{8	extsf{H}}$                     | 2.4   | 1   |                     | lv       |

| Input current                                                                                  | $V_{8L}$                             |       |     | 0.8                 | ٧        |

| $V_{8H} = 5 \text{ V}$ $V_{8L} = 0.4 \text{ V}$                                                | $I_{	t 8	t H}$ $I_{	t 8	t L}$        |       |     | 8<br>-550           | μA<br>μA |

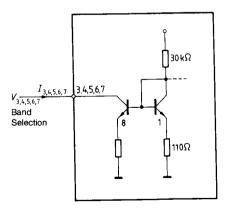

| Band select outputs Reverse current                                                            | $I_{3H}$                             | ì     | 1   | 1.0                 |          |

| $V_{3H} = 15 \text{ V}$ Current drain                                                          | $I_{3	ext{H}}$                       | 0.5   |     | 10                  | μΑ       |

| 2 V ≤ V <sub>3</sub> ≤ 15 V                                                                    | <b>1</b> 3H                          | 0.5   |     | 3                   | mA       |

| Tuning section PD, $V_{\rm D}$ , $I_{\rm REF}$ , LOCK Charge pump current                      | $I_{13}$                             | ± 250 | ı   | 1 , 550             |          |

| $I_{\text{pump}} = 10 \text{ x } I_{\text{REF}}, V_{\text{S}} = 5 \text{ V}$<br>Tuning voltage |                                      | 1250  |     | ± 550               | μΑ       |

| $I_{15L} = 1.5 \text{ mA}$                                                                     | V <sub>15L</sub>                     | į.    |     | 0.3                 | V        |

| Reverse current $V_{15H} = 33 \text{ V}$                                                       | $I_{ m 15H}$                         |       |     | 20                  | μА       |

| Reference current<br>ext. $R = 120 \text{ k}\Omega$ ; $V_S = 5 \text{ V}$                      | $I_{14}$                             | 30    |     | 40                  | μА       |

| Output voltage int. $R_L = 3 \text{ k}\Omega$                                                  | V <sub>12 H</sub>                    | 4.5   |     |                     | V        |

| $I_{12H} = -100 \mu\text{A}$<br>$I_{12L} = 100 \mu\text{A}$                                    | V <sub>12 L</sub>                    |       |     | 0.7                 | v        |

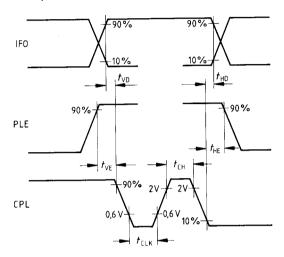

| IFO, PLE<br>Set-up time for                                                                    |                                      |       |     |                     |          |

| enable<br>data                                                                                 | $t_{VE}$                             | 2     |     |                     | μs       |

| Hold time for:                                                                                 | $t_{VD}$                             | 2     |     |                     | μs       |

| enable<br>data : 5                                                                             | $t_{\sf HE}$                         | 2 2   |     |                     | μs<br>μs |

| CPL                                                                                            |                                      |       |     |                     |          |

| H pulse width<br>L pulse width                                                                 | t <sub>CH</sub><br>t <sub>CL</sub>   | 2 2   |     |                     | μs<br>μs |

## Circuit description

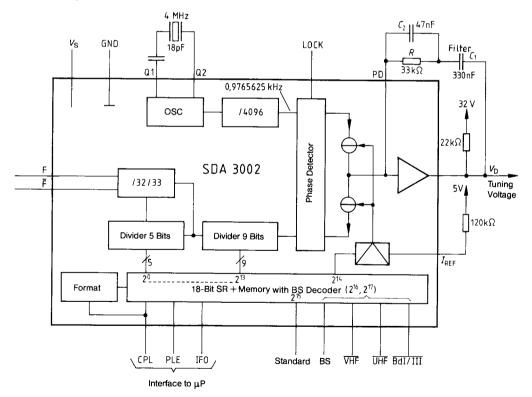

Triggered by the ECL inputs F/F a switchable 32/33 counter operates as a 14-bit synchronous divider in the dual modulus method when combined with a 5 and 9-bit programmable synchronous counter. In this combination the 5-bit counter controls the switch-over from 32 to 33 (block diagram 1). Dividing ratios of N = 1024 to 16383 are possible.

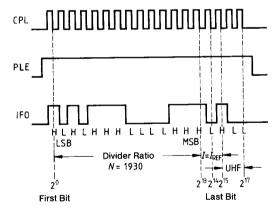

The 18-bit deep shift register with latch is subdivided into 14 bits for storing the dividing ratio *N*, as well as 1 bit for selecting the pump current and 1 bit for a standard switch-over. The remaining 2 bits control the 4 band selection outputs. The message is inserted over the serial data input IFO with the H-L slope of the shift clock CPL, when the enable input is set at H. Beginning with LSB, the complement of the dividing ratio is inserted in binary code, then the select bit 2<sup>14</sup> for the pump current and the control bit 2<sup>15</sup> for standard TV switch-over are added. The band selection control bits 2<sup>16</sup> and 2<sup>17</sup> complete this process (refer to table).

An integrated control circuit checks the world length (18 bits) of the data message. The 18-bit latch accepts the data from the shift register during the L state of the enable input PLE.

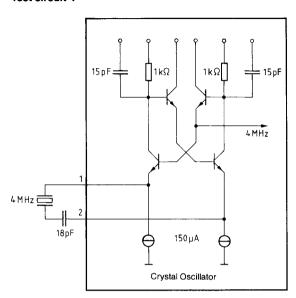

A 4 MHz crystal controlled clock oscillator has been integrated in the IC. An internal reference divider divides the output signal of the crystal oscillator ( $f_{\rm OSC}=4$  MHz) by 4096 resulting in 0.97656 kHz (reference signal), providing a frequency resolution of 62.5 kHz by means of the asynchronous permanent divider (dividing factor 64).

In a digital phase detector the divided VCO input signal is compared with the reference signal. If the trailing edge of the VCO input signal appears before the trailing edge of the reference signal, the output DOWN of the phase detector will be in the H state for the duration of the phase difference. However, if above signal sequence is reversed, the output UP will be in the H state instead. The outputs UP/DOWN control the two current sources I+ and I- (charge pump). In case both outputs are in the L state, the charge pump output will be in the high impedance mode (TRISTATE). Information with respect to either the H or L state will be provided at the LOCK output by the logical "NOR" of the outputs UP/DOWN.

The output current of the charge pump (source current = drain current) is adjusted by an external resistor between pin  $I_{\rm REF}$  and  $V_{\rm CC}$ . In addition, this output current can be generated by the control bit for the pump current at the same value or at a value increased by a factor of 10 (refer to table).

The current pulses generated by the charge pump are integrated into the tuning voltage by means of an active low pass filter (on-chip loop amplifier and external RC circuit). The dc output signal of the low pass filter is available at  $V_{\rm D}$  and is used as tuning voltage for the VCO. In order to provide tuning voltages higher than  $V_{\rm CC}=5$  V, the output stage of the amplifier consists of a transistor with an open collector. The external collector resistor can be connected to voltage up to 33 V.

To switch voltages higher than  $V_{\rm CC}=5$  V, the band selection outputs (Bd I/III, VHF, UHF, Standard, BS) include current drains with open collectors. It is therefore possible to directly connect transistors operating as band selection switches without the use of current limiting resistors (please refer to application circuit).

## Pin description

| Pin | Symbol                          | Function                           |  |  |  |

|-----|---------------------------------|------------------------------------|--|--|--|

| 1   | Q1                              | Crystal                            |  |  |  |

| 2   | Q2                              | Crystal                            |  |  |  |

| 3   | Standard                        | Standard switchover output         |  |  |  |

| 4   | BS                              | Band selection output BS           |  |  |  |

| 5   | VHF                             | Band selection output VHF          |  |  |  |

| 6   | UHF                             | Band selection output UHF          |  |  |  |

| 7   | Bd I/III                        | Band selection output I/III        |  |  |  |

| 8   | PLE                             | Enable input for shift register    |  |  |  |

| 9   | GND                             | Ground                             |  |  |  |

| 10  | CPL                             | Shift clock pulse input            |  |  |  |

| 11  | IFO                             | Data input                         |  |  |  |

| 12  | LOCK                            | Lock output                        |  |  |  |

| 13  | PD                              | Amplifier input/charge pump output |  |  |  |

| 14  | $I_{REF}$                       | Current adjustment for charge pump |  |  |  |

| 15  | $ V_{\scriptscriptstyle  m D} $ | Tuning voltage output              |  |  |  |

| 16  | F                               | Signal input                       |  |  |  |

| 17  | F                               | Signal input                       |  |  |  |

| 18  | <b>V</b> <sub>S</sub>           | Supply voltage                     |  |  |  |

### Truth table

| Pump current                          | IFO-Bit<br>2 <sup>14</sup> | Bit 2 <sup>15</sup> | Output<br>Standard |

|---------------------------------------|----------------------------|---------------------|--------------------|

| $I = I_{REF}$ $I = 10 \times I_{REF}$ | L<br>H                     |                     | L<br>H             |

| IFO-Bit         | t                | Band se     | electior    | outputs     | *)          | Meaning                             |

|-----------------|------------------|-------------|-------------|-------------|-------------|-------------------------------------|

| 2 <sup>16</sup> | 2 <sup>17</sup>  | Bd I/III    | VHF         | UHF         | BS          |                                     |

| L<br>L<br>H     | L<br>H<br>L<br>H | H<br>H<br>L | H<br>L<br>L | L<br>H<br>H | H<br>H<br>L | UHF<br>VHF/Bd I<br>VHF/Bd III<br>BS |

# Pulse diagram

**111**

<sup>\*)</sup> L - conductive; H - blocking

### Computation for loop filter

#### Example for channel 47

$$P=64$$

;  $N=11520$ ;  $I_{\rm p}=200$  μA;  $K_{\rm VCO}=18.7$  MHz/V;  $R=33$  kΩ;  $C_{\rm 1}=330$  nF  $\omega_{\rm R}=124$  Hz;  $f_{\rm R}=20$  Hz;  $\xi=0.675$

Standard dimensioning:  $C_2 \approx C_{1/5}$

### **Block diagram**

# Pulse diagram

# Set-up and hold times

### Test and measurement circuits

### Test circuit 1

### Test circuit 2

### Test circuit 3

### Test circuit 4

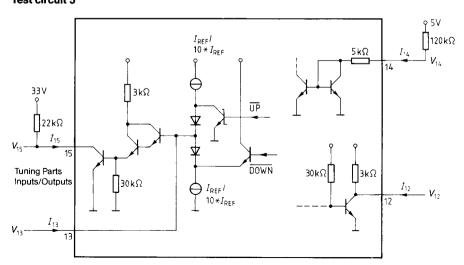

## Test circuit 5

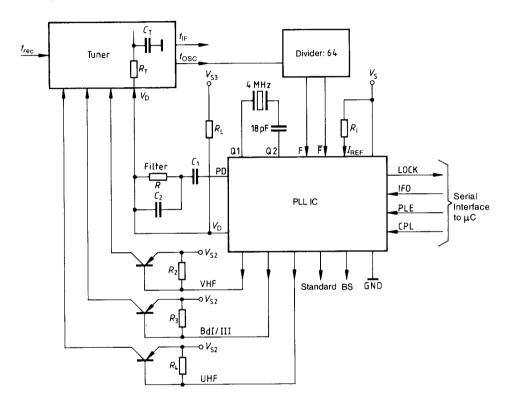

### **Application circuit**

$R_1 = 120 \text{ k}\Omega (I_P = 35/350 \text{ }\mu\text{A})$ Dimensional proposal:

$R_{L} = 22 \text{ k}\Omega; R_{2}...R_{4} = 22 \text{ k}\Omega$   $R = 33 \text{ k}\Omega; C_{1} = 330 \text{ nF}; C_{2} = 47 \text{ nF}$ Loop filter:

$R_{\rm T} = 10 \, \text{k}\Omega; \, C_{\rm T} = 47 \, \text{nF}$ Filter (in tuner):